JLPEA | Free Full-Text | Low Power Testing—What Can Commercial Design-for-Test Tools Provide? | HTML

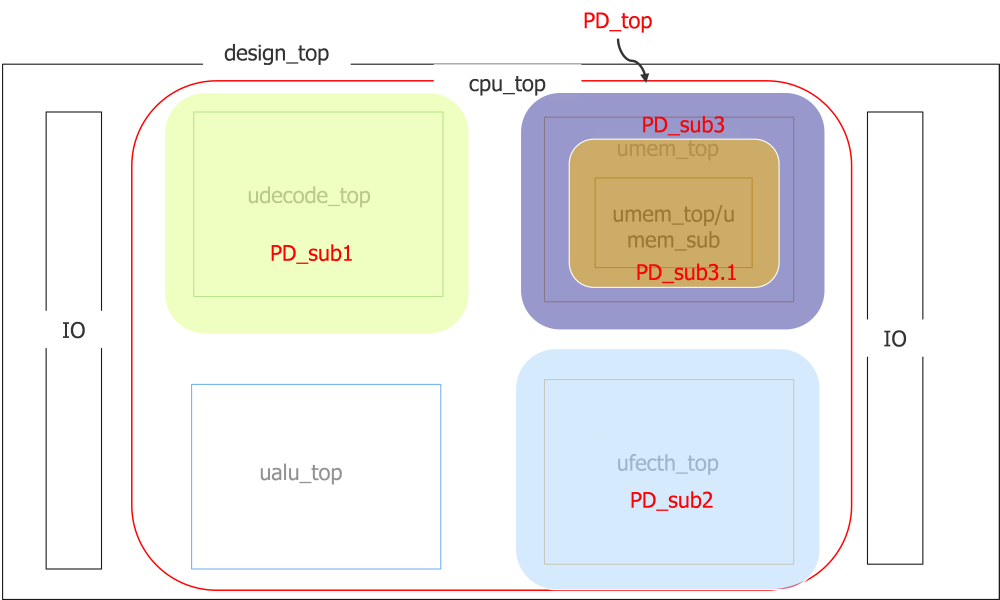

details the structure of the AO_PD (power domain 0) layer of Fig. 1.... | Download Scientific Diagram

Illustration of power-domain NOMA principles. User 2 is with better... | Download Scientific Diagram